Electrical Wire

Picazzo contains a simple electrical wire template, which can be used to include simple electrical wires in your circuit.

ElectricalWireTemplate

- class picazzo3.traces.electrical_wire.ElectricalWireTemplate

- Parameters:

- name: String that contains only ISO/IEC 8859-1 (extended ASCII py3) or pure ASCII (py2) characters

The unique name of the pcell

Views

- class Layout

- Parameters:

- purpose: PatternPurpose

drawing purpose for the wire

- process: ProcessLayer

process for the wire

- windows: List with type restriction, allowed types: <class ‘ipkiss3.pcell.trace.window.window._TraceWindow’>

List of Trace Windows that know how to draw themselves relative to the shape of the Trace

- layer: __Layer__

- pin_shape: Shape

shape to be used for the pins

- trace_template_for_ports: _TraceTemplate.Layout

Trace template to be used for the ports. Default = this template

- control_shape_layer: __Layer__

layer on which the control shape is drawn

- draw_control_shape: ( bool, bool_ or int )

draws the control shape on top of the waveguide

- width: float and number > 0

Width of the electrical trace

- view_name: String that contains only alphanumeric characters from the ASCII set or contains _$. ASCII set is extended on PY3.

The name of the view

Examples

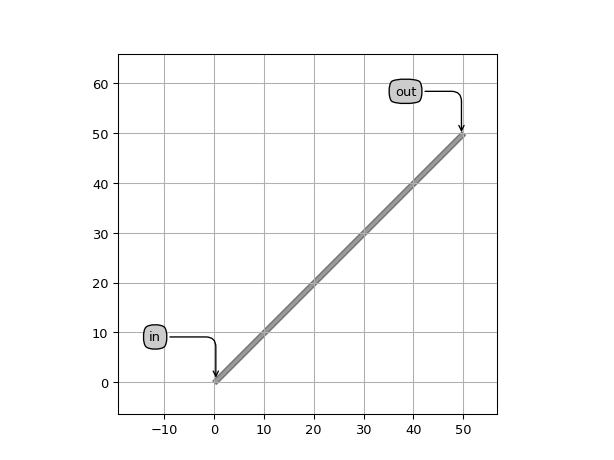

""" In a lot of simple cases you can just use the default wire template that is specified in the technology file. """ import si_fab.all as pdk # noqa: F401 from ipkiss3.pcell.wiring import ElectricalWire # This uses the default trace template defined in the tech file wire = ElectricalWire() layout = wire.Layout(shape=[(0, 0), (50, 50)]) layout.visualize(annotate=True)

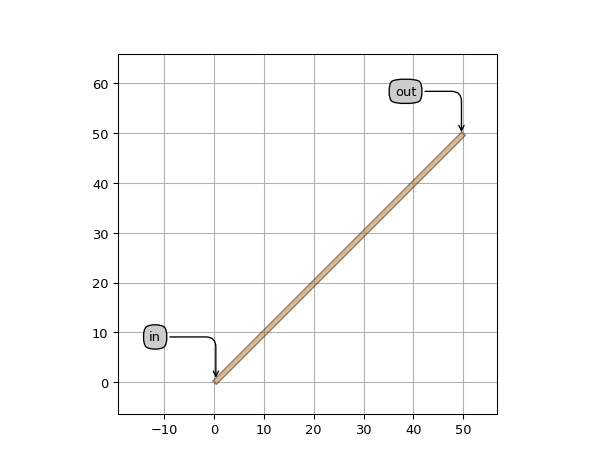

""" If the default wire template is not sufficient, you can always create your own template. In this example we show how to create a template with a non-default width. """ import si_fab.all as pdk # noqa: F401 from ipkiss3.pcell.wiring import ElectricalWire from picazzo3.traces.electrical_wire import ElectricalWireTemplate etpl = ElectricalWireTemplate() etpl.Layout(width=4.0) # This uses the default trace template defined in the tech file wire = ElectricalWire(trace_template=etpl) layout = wire.Layout(shape=[(0, 0), (50, 50)]) layout.visualize(annotate=True)

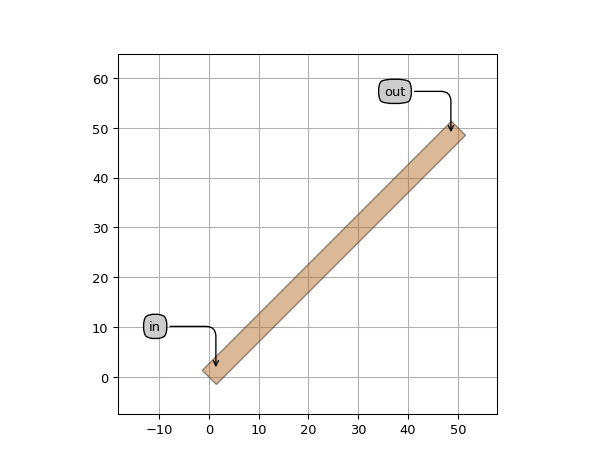

""" It's also possible to specify a custom process to draw the wire. """ import si_fab.all as pdk # noqa: F401 from ipkiss3.pcell.wiring import ElectricalWire from picazzo3.traces.electrical_wire import ElectricalWireTemplate from ipkiss.process import ProcessLayer etpl = ElectricalWireTemplate() my_process = ProcessLayer("My Special Process", "MSP") etpl.Layout(process=my_process) # This uses the default trace template defined in the tech file wire = ElectricalWire(trace_template=etpl) layout = wire.Layout(shape=[(0, 0), (50, 50)]) layout.visualize(annotate=True)