ExtendPorts

- class picazzo3.container.extend_ports.ExtendPorts

Extends all the ports listed in

port_labelswith a waveguide of a given length.This length is specified in

extension_lengthof the Layout View.A common trace template for all ports is specified through

trace_template. When this is set to None (the default), the trace templates of the ports of the contents will be used.- Parameters:

- trace_template: ( PCell and _WaveguideTemplate ), *None allowed*

Template for all ports. If None, the trace templates of the ports will be used

- waveguides: List with type restriction, allowed types: <class ‘ipkiss3.pcell.cell.pcell.PCell’>

waveguides added to the contents

- auto_transition: ( bool, bool_ or int )

If True, automatically transition all ports of contents to the given trace template. If False, no transitions are applied, which might lead to a discontinuity in the waveguide. Also, if trace_template is None, no transitions are applied.

- port_labels: ( List with type restriction, allowed types: <class ‘str’> ), *None allowed*

Labels of the ports to be processed. Set to None to process all ports.

- external_port_names: str

Dictionary for remapping of the port names of the contents to the external ports

- contents: PCell

the contents of the container: the child cell

- name: String that contains only ISO/IEC 8859-1 (extended ASCII py3) or pure ASCII (py2) characters

The unique name of the pcell

- Other Parameters:

- bundle: ( PCell ), locked, *None allowed*

bundle of waveguides added to the contents, generated based on the supplied waveguides list

- trace_templates: List with type restriction, allowed types: <class ‘ipkiss3.pcell.cell.pcell.PCell’>, locked

list of templates to apply to all ports

Views

- class Layout

- Parameters:

- extension_length: float and number > 0

Length by which the ports are extended

- area_layer_on: ( bool, bool_ or int )

When True, the waveguide area will be covered by i3.Rectangles on all cover layers.

- routes:

routes along which the waveguides will be generated

- contents_transformation: GenericNoDistortTransform

transformation to apply to the contents

- flatten_contents: ( bool, bool_ or int )

if True, it will insert the contents as elements in the layout, rather than as an Instance

- view_name: String that contains only alphanumeric characters from the ASCII set or contains _$. ASCII set is extended on PY3.

The name of the view

- Other Parameters:

- extension_lengths: locked

Examples

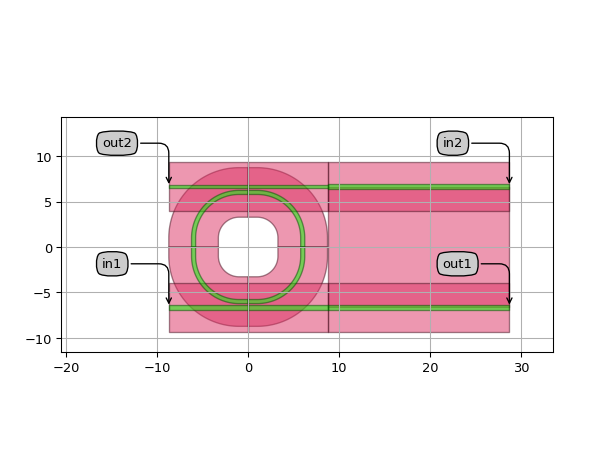

import si_fab.all as pdk # noqa: F401 from picazzo3.filters.ring import RingRect180DropFilter from picazzo3.traces.wire_wg import WireWaveguideTemplate from picazzo3.container.extend_ports import ExtendPorts wg_t1 = WireWaveguideTemplate() wg_t1.Layout(core_width=0.55) wg_t2 = WireWaveguideTemplate() wg_t2.Layout(core_width=0.35) my_ring = RingRect180DropFilter(name="ring_for_fanout", coupler_trace_templates=[wg_t1, wg_t2]) my_ring.Layout() port_labels = ["E1", "E0"] my_container = ExtendPorts(contents=my_ring, port_labels=port_labels, auto_transition=True) layout = my_container.Layout(extension_length=20.0, area_layer_on=False) layout.visualize(annotate=True)

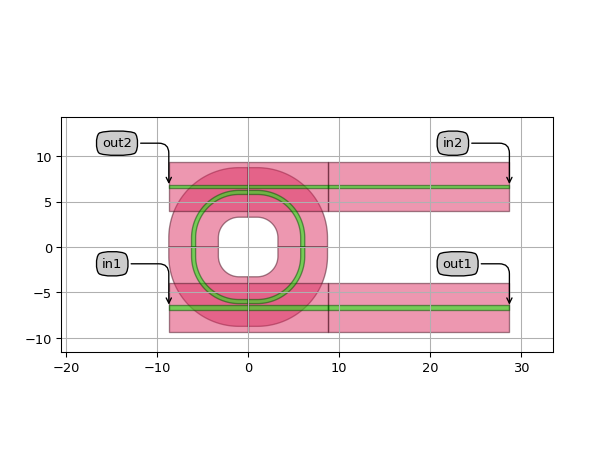

import si_fab.all as pdk # noqa: F401 from picazzo3.filters.ring import RingRect180DropFilter from picazzo3.traces.wire_wg import WireWaveguideTemplate from picazzo3.container.extend_ports import ExtendPorts wg_t1 = WireWaveguideTemplate() wg_t1.Layout(core_width=0.55) wg_t2 = WireWaveguideTemplate() wg_t2.Layout(core_width=0.35) my_ring = RingRect180DropFilter(name="ring_for_fanout", coupler_trace_templates=[wg_t1, wg_t2]) my_ring.Layout() port_labels = ["E1", "E0"] my_container = ExtendPorts( contents=my_ring, port_labels=port_labels, trace_template=wg_t1, auto_transition=False # Default ) layout = my_container.Layout(extension_length=20.0, area_layer_on=True) layout.visualize(annotate=True)